#### DKT217 COMPUTER SYSTEM TOPUP MTE DATE : FRIDAY 10 APRIL 2020 TIME : 9.30am ~ 11.00am DURATION : 1 HOUR 30 MINUTES UPLOAD CUT-OFF : 11.02am

## **ANSWER ALL QUESTIONS**

#### **QUESTION 1**

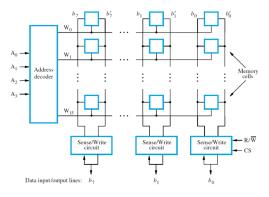

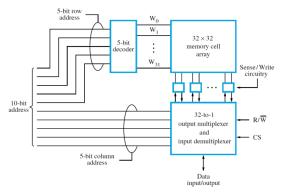

a) A 1K-bit memory cell can be organized into 128x8 or 1024x1 arrays. Draw the block diagram for both memory organization.

(5 marks)

#### SOLUTION

128 x 8 array organization (8-bit output)

Using 7 to 128 bit decoder

1024 x 1 array organization (1-bit output)

[SULIT]

#### **QUESTION 2**

An 8-bit data E8H is to be stored into the memory.

- a) Find the Kin code when the data is stored into the memory.

- b) Find the Kout code when the data is taken out from the memory if the data becomes ECH.

- c) Determine the syndrome which proves the location of the faulty bit from the 8-bit data.

#### SOLUTION

Finding K-bits :

$2^{K} - 1 \ge M + K \rightarrow$  try and error we get K=4 bits when M is 8.

So:

| Locations in           | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4              | 3    | 2    | 1              |

|------------------------|------|------|------|------|------|------|------|------|----------------|------|------|----------------|

| decimal and<br>binary  | 1100 | 1011 | 1010 | 1001 | 1000 | 0111 | 0110 | 0101 | 0100           | 0011 | 0010 | 0001           |

| M & K bit<br>positions | M7   | M6   | M5   | M4   | Кз   | M3   | M2   | M1   | K <sub>2</sub> | M0   | K1   | K <sub>0</sub> |

| Data In<br>E8H         | 1    | 1    | 1    | 0    |      | 1    | 0    | 0    |                | 0    |      |                |

| Data Out<br>ECH        | 1    | 1    | 1    | 0    |      | 1    | 1    | 0    |                | 0    |      |                |

a) Finding Kin code values :

| $K0 = M0 \oplus M1 \oplus M3 \oplus M4 \oplus M6$ | => 0 |

|---------------------------------------------------|------|

| $K1 = M0 \oplus M2 \oplus M3 \oplus M5 \oplus M6$ | => 1 |

| $K2 = M1 \oplus M2 \oplus M3 \oplus M7$           | => 0 |

| K3 = M4 $\oplus$ M5 $\oplus$ M6 $\oplus$ M7       | => 1 |

Thus, the exact data E8H (11101000B) to be stored into memory is EC2H (111011000010B), but the question only asks for the Kin code which is **1010B**.

b) Finding Kout code values :

| $K0=M0\oplusM1\oplusM3\oplusM4\oplusM6$           | => 0 |

|---------------------------------------------------|------|

| $K1 = M0 \oplus M2 \oplus M3 \oplus M5 \oplus M6$ | => 0 |

| $K2 = M1 \oplus M2 \oplus M3 \oplus M7$           | => 1 |

| $K3 = M4 \oplus M5 \oplus M6 \oplus M7$           | => 1 |

| in the event date FCU (11101100                   |      |

Thus, the exact data ECH (11101100B) to be loaded from memory is EE8H (111011101000B), but the question only asks for the Kout code which is **1100B**.

c) Getting the syndrome which points to location of the faulty bit :

| Kin          | 1010                                                               |

|--------------|--------------------------------------------------------------------|

| <u>⊕Kout</u> | <u>1100</u>                                                        |

| Syndrome     | 0110 $\leftarrow$ this is the table location that refers to M2 bit |

The syndrome points to M2 which shows the value differences when storing (0) and when loading (1).

[5 marks]

[SULIT]

## **QUESTION 3**

- a) Assume a computer has the memory with the size of 16MB and a cache size of 64KB that addresses at the byte level. If the computer's cache line can contain 16 bytes, determine the format sizes of the following cache map :

- (i) Direct Mapped Cache

- (ii) Associative Mapped Cache

- (iii) 2-way Set Associative Mapped Cache

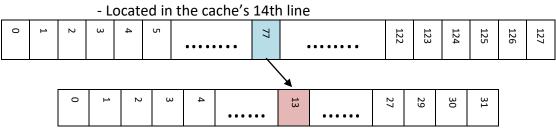

- b) Assuming a memory has 128 blocks and a cache consists of 32 lines. Determine where the 78<sup>th</sup> memory block will be located in the cache for :

- (i) Direct Mapped Cache

- (ii) Associative Mapped Cache

- (iii) 4-way Set Associative Mapped Cache

#### SOLUTION

a) Memory size is 16MB, expressed in the power of 2 is 2<sup>24</sup>, Cache size is 64KB, expressed in the power of 2 is 2<sup>16</sup>, Cache line size is 16B, expressed in the power of 2 is 2<sup>4</sup>,

| (i)  | Direct Mapped Ca<br>- Total addressab<br>- Cache line size, v<br>- Total addressab<br>- Addressable cac<br>- Block format<br>Tag, s-r<br>8 | le bits, s+w = 24<br>w = 4<br>le cache lines, r+v | v = 16<br>Size, w<br>4 |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------|--|--|

| (ii) | Associative Mapped Cache                                                                                                                   |                                                   |                        |  |  |

- Total addressable bits, s+w = 24

- Cache line size, w = 4

- No addressable cache lines needed, just total tag, s

- Block format

24 bit (s+w)

| Tag, s | Size, w |

|--------|---------|

| 20     | 4       |

- (iii) 2-way Set Associative Mapped Cache

- Total addressable bits, s+w = 24

- Cache line size, w = 4

- Total addressable cache lines, r+w = 16

- X-way addressable, 2<sup>k</sup>, k =1

- Addressable set bits, d = r-1 = 11

- Block format

| 21 | hit |       |

|----|-----|-------|

| 24 | DIL | (s+w) |

| Tag, s-d | Set, d | Size, w |

|----------|--------|---------|

| 9        | 11     | 4       |

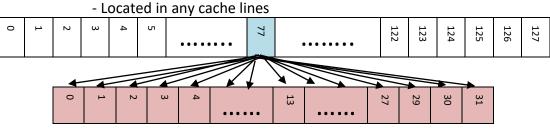

- b) Memory blocks = 128

Cache lines = 32

Location for memory block 78 inside the cache using :

- (i) Direct Mapped

\_\_\_\_

# (ii) Associative Mapped

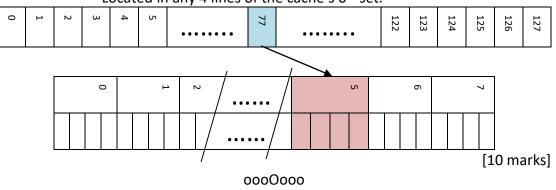

(iii) 4-way Set Associative Mapped

Located in any 4 lines of the cache's 6<sup>th</sup> set.

[SULIT]